写在前面的话#

念叨一句“I can’t breathe”,老美的骚乱还在蔓延,动静比那时候的HK还大,*近看了很多评论大家对国际局势,种族矛盾等专题,脑子混乱,慢慢消化下...

写点技术类小文,平静下。相比大骚乱,我更应该更关心下,猪肉明天还涨价吗?

对于低速率的100M/1GE网络损伤仿真,基本使用X86的架构跑个开源的软件,基本也能够在网卡NIC上构建一个简易的损伤环境,简单实现丢包/延迟/错误注入都没有问题,性能能做到多强,基本要看NIC后端的PC的CPU性能,这块主要吃CPU能力。

如果优化做得好,调度合理,配合较强性能的X86主机,基本在10GE速率也能够实现个七七八八。懒得动手的,对损伤粒度,损伤类型有较高要求的测试,也有很多商用方案选择:IWL,Apposite,HoloWAN,Packetstorm ,etc.

- 25G/50G/100G高速网络损伤仿真为什么需要纯硬件盒子实现?

- 为什么在高速链路下X86不香了?

但是到了25G/50G/100G高速链路时间, 28Gbps/ lane SerDes的高速数据并发,要处理如此庞大的数据流,我们会需要多个CPU来介入,我们把所有的CPU资源都抢走了,系统本身怎么办?这部分我觉得可以去看看“智能网卡SmartNIC”相关的文章,解释得很清楚,这里就不赘述了(小编这部分忽悠不来,哈哈哈哈哈哈)。简单来说,就是1G/10G时间,比如1个GbE的流量我们用1个CPU核心进行任务绑定,那么10GbE占用了10个,那么强如28核心的X86系统依旧有18个CPU核心处理其他事务,而到了25GbE,我们就只剩下3个核心来跑系统了,...这就很尴尬了

##插入一个话题,为什么我不把40GE也纳入到高速网络接口中来?

因为我认为40GbE = 4 Lane x 10GbE,好像跟10GbE没啥大区别吧,...

因为在25/50/100GbE速率下,我们没法分配那么多CPU资源以满足NIC的计算能力,所以我们需要引入异构计算加速。比如在NIC上面价格ARM处理器来进行任务分担,加个SoC进行任务协处理,加个FPGA来进行算力弥补,具体可以参考下赛灵思新出的SmartNIC U25的相关介绍,解释得很清楚。

异构加速方案,*快速容易搭建的就是NIC+FPGA的方案了,开发周期短,灵活性高,可重构,价格不便宜但可以接受。

所以呢,毋庸置疑,我们目前拿到的Chimera-100G多速率网络损伤仿真模拟测试仪将会是个内置FPGA的方案。

无图无真相!放大一下,看下细节! ===>

>>>>>>>

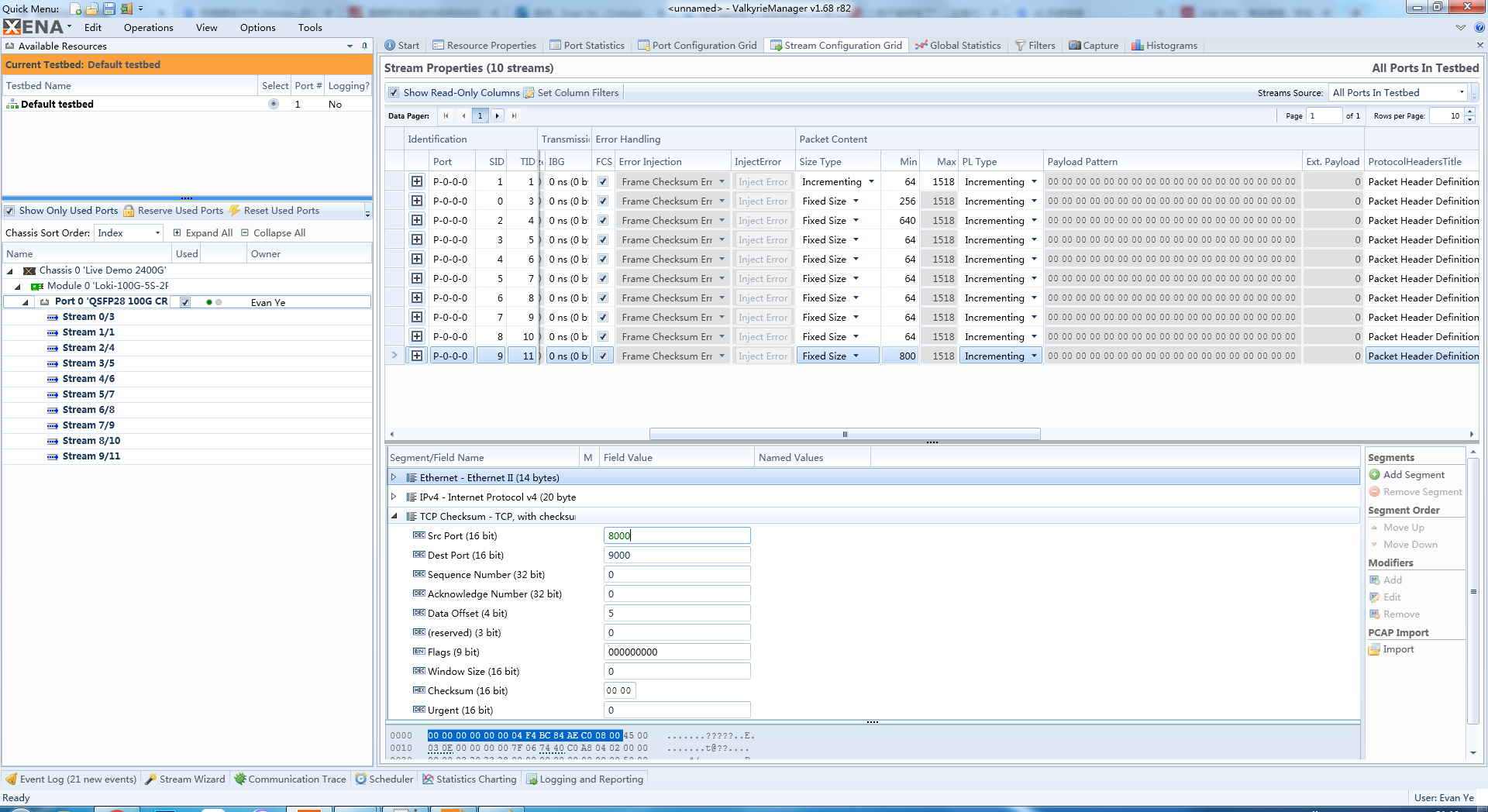

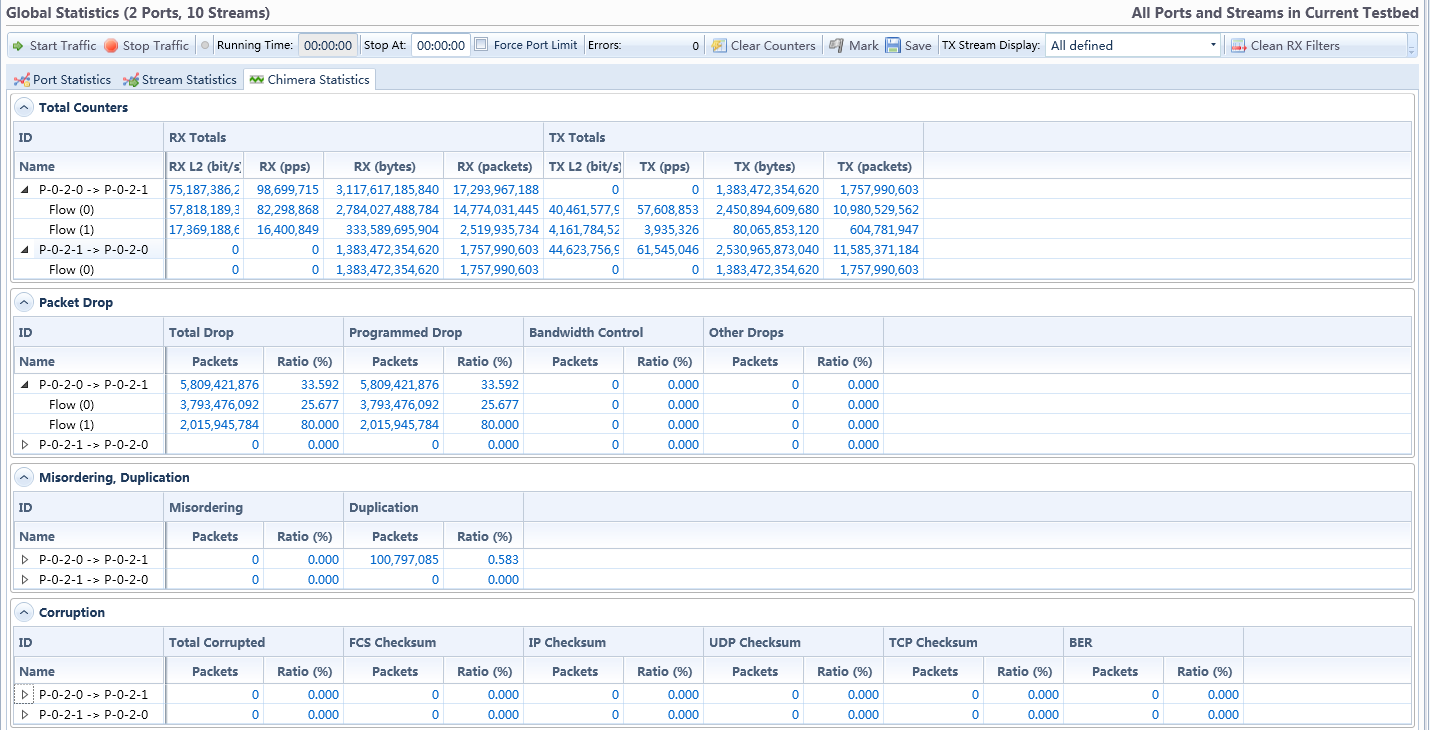

1.使用Valkyrie-Loki PG板卡进行50GbE速率下的多流数据的收发模拟,模拟64/1518Byte,IP、UDP等不同报文类型,是否加VLAN tag等进行Multi-Streams Tx/Rx

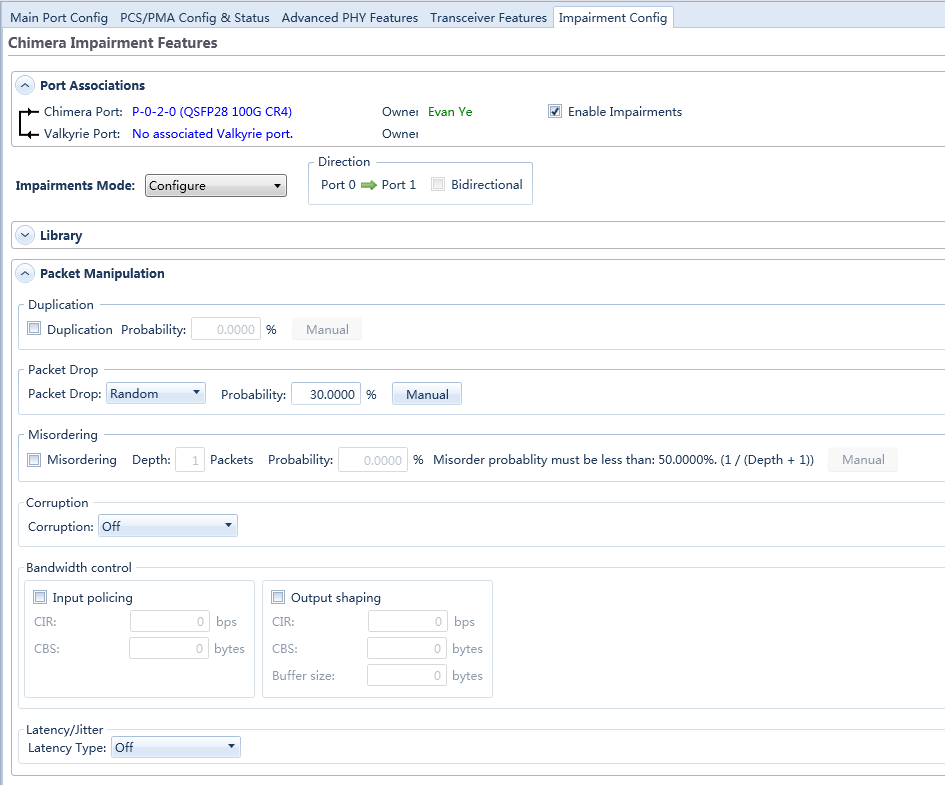

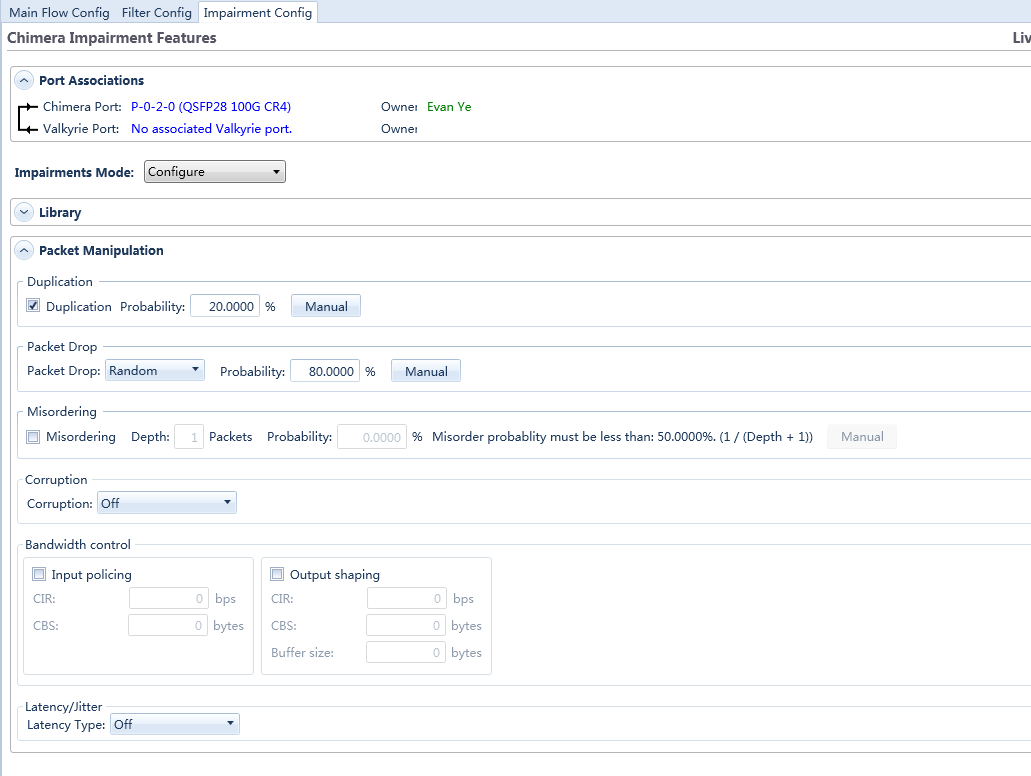

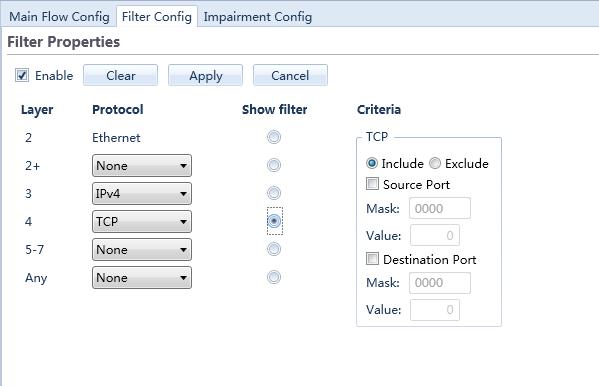

2.使能Chimera-100G网络损伤仿真测试仪,使其链接到50GbE模式下,进行多个Flow的损伤设定(单端口支持8 Flows)

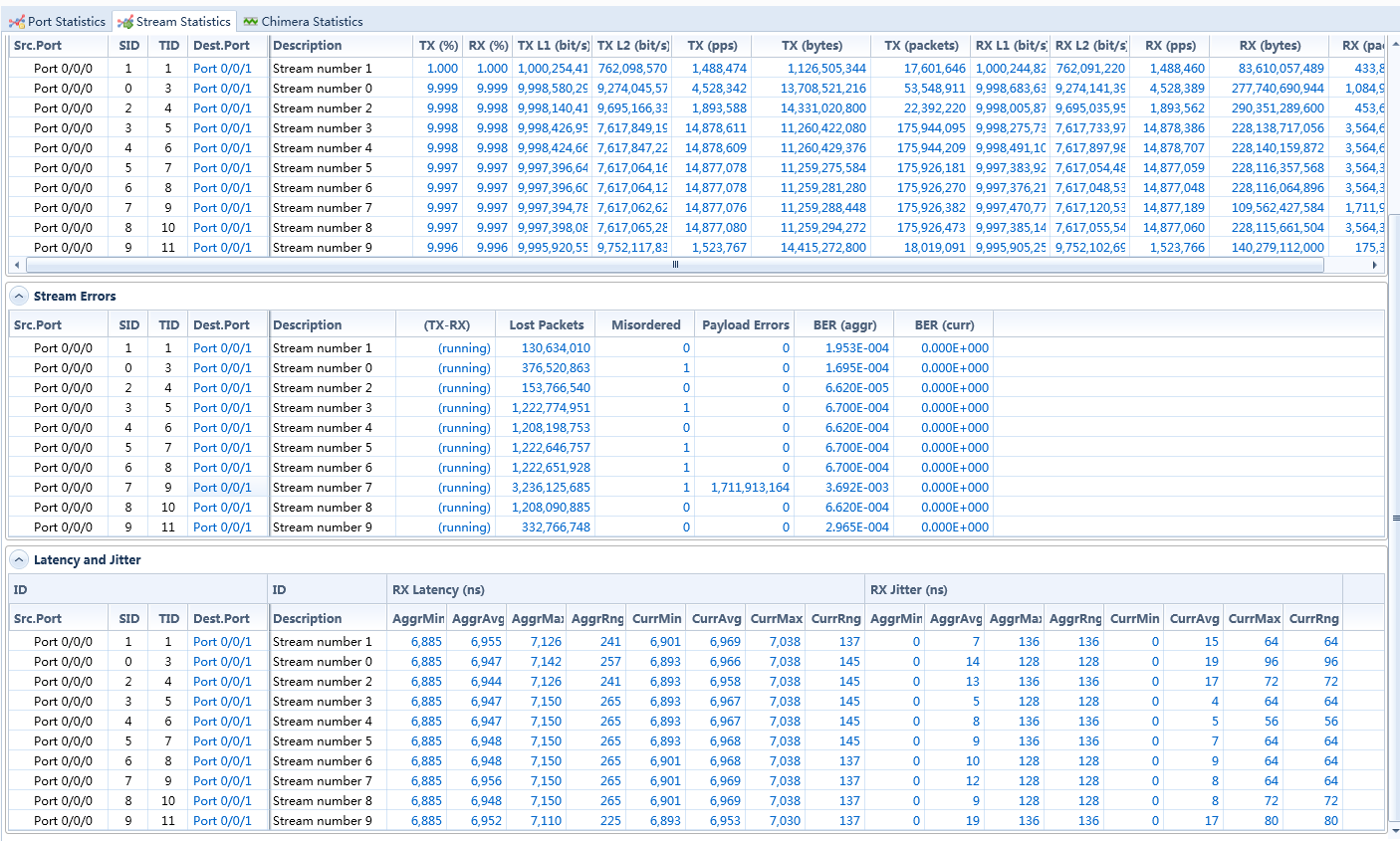

3.观察Chimera-50G损伤规则禁用情况下的端口Rx信息统计

4.观察使能了其中损伤仿真的Flow情况下的端口Rx信息统计

5.观察全部损伤仿真的Flows都使能情况下的Rx信息统计

6.尝试只对PTP时间相关协议进行特定损伤追踪

7.切换成25G,100G进行相同的测试实验

8.凑个第8点,写啥不重要了,要凑8点很重要!

上点小图(感觉效果不是很好,打算后面出个视频版本的,发里,也许我可以注册Bilibili试试)